National Aeronautics and Space Administration

Armstrong Flight Research Center

# X-57 Maxwell

# High Lift Propeller Indicator and Control Requirements Document

# REQ-CEPT-029

| Rev: -       | <b>Date:</b> 1                              | 7 June 2021                                                                  |

|--------------|---------------------------------------------|------------------------------------------------------------------------------|

| Prepared By: | //SIGNED//                                  | Digitally signed by CLAUDIA<br>Sales<br>Date: 2021.06.17 10:58:48 -07'00'    |

|              | Claudia Sales/AFRC<br>X-57 Deputy Chief E   |                                                                              |

| Approved By: | //SIGNED//                                  | 2021.06.23                                                                   |

|              | Sean Clarke/AFRC<br>X-57 Power and Com      | Date<br>nmand IPT Lead                                                       |

|              | ETHAN<br>BAUMANN 🥢                          | Digitally signed by ETHAN<br>BAUMANN<br>Date: 2021.06.24 06:09:37<br>-07'00' |

|              | Ethan Baumann/ AFF<br>X-57 Maxwell Chief E  |                                                                              |

|              | Vincent Schultz                             | gitally signed by Vincent Schultz<br>ate: 2021.06.24 11:41:06 -04'00'        |

|              | Heather Maliska/ AFF<br>X-57 Project manage |                                                                              |

|              | //SIGNED//                                  | Digitally signed by<br>FRANKLIN HARRIS<br>Date: 2021.06.23 18:06:08          |

|              | Keith Harris / AFRC<br>X-57 Vehicle IPT Lea | Date                                                                         |

#### **REVISION HISTORY**

| Rev          | DATE      | DESCRIPTION     |

|--------------|-----------|-----------------|

| ( <b>*</b> ) | 6/17/2021 | Initial release |

|              |           |                 |

|              | -         |                 |

|              |           |                 |

|              |           |                 |

|              |           |                 |

|              | -         |                 |

|              |           |                 |

| 1            |           |                 |

|              |           |                 |

|              |           |                 |

|              |           |                 |

#### **Table of Contents**

| 1  | Sco  | pe                                                       | . 3 |

|----|------|----------------------------------------------------------|-----|

| 2  |      | em Description                                           |     |

| 1  | 2.1  | System Diagram                                           | . 4 |

| 3  |      | licable Documents                                        |     |

| 4  | Req  | uirements Standards                                      | . 6 |

| 5  | Req  | uirements Verification Methods                           | . 7 |

| ;  | 5.1  | Verification Method - Inspection                         | . 7 |

| ļ  | 5.2  | Verification Method - Analysis                           | . 7 |

|    | 5.3  | Verification Method - Test                               | . 7 |

| ł  | 5.4  | Verification Method - Demonstration                      | . 8 |

| 6  | High | Lift Propeller Control (HiPC) Requirements               | . 9 |

| (  | 6.1  | HiPC Interface Requirements                              | . 9 |

|    | 6.2  | HiPC Cockpit Requirements                                | 16  |

| 7  | High | n Lift Propeller Indicator (HiPI) Requirements           | 18  |

| 8  | 7.1  | HiPI Interface Requirements                              | 18  |

|    | 7.2  | HiPI Cockpit Status Indicator Requirements               | 23  |

| 8  | HiPI | and HiPC Combined Requirements                           | 26  |

|    | 8.1  | Power Requirements                                       | 26  |

|    | 8.2  | Weight Requirements                                      | 27  |

|    | 8.3  | Environmental Test Requirements                          | 28  |

|    | 8.4  | Structural Requirements                                  | 28  |

| į, | 8.5  | Fabrication Requirements                                 | 28  |

|    | 8.6  | Derating of Electrical and Electronic Parts Requirements | 30  |

#### Table of Figures

| Figure 1 – High Lift Propulsor Distribution          | 4 |

|------------------------------------------------------|---|

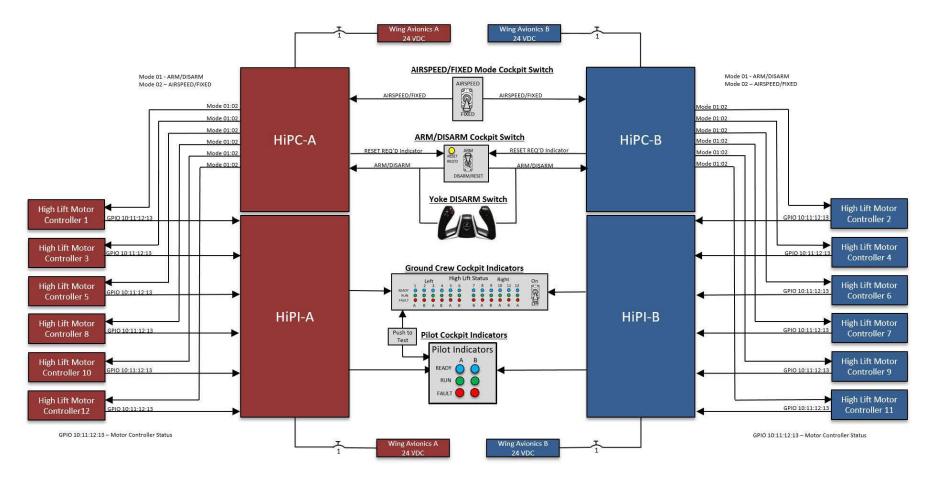

| Figure 2 – HiPI & HiPC Block Diagram with Interfaces | 5 |

# 1 Scope

This document establishes the interface requirements for the X-57 High Lift Propeller Control (HiPC) and the High Lift Propeller Indicator (HiPI) subsystems.

# 2 System Description

The HiPI and HiPC shall follow the A/B system architecture for the X-57 aircraft. The A/B architecture is utilized by flight critical systems including the high lift propulsors (high lift propeller, high lift motor and high lift motor controller). This architecture provides redundancy in the event of an A system failure or a B system failure. The A and B high lift propulsors are distributed across the left and right wing so that a failure of an A system or B system will not produce an abrupt asymmetric thrust event and cause an adverse yaw condition for the aircraft. See **Figure 1** for the high lift propulsors

The HiPI and HiPC provide the indication and control interfaces between the X-57 cockpit and the 12 High lift motor controllers (HLMCs). **Figure 2** provides a block diagram of this system.

Six HLMCs on the A system will provide controller status inputs to HiPI-A and six HLMCs on the B system will provide controller status inputs to HiPI-B. HiPI-A and HiPI-B will process these controller inputs to provide the status of all 12 HLMCs to the pilot and ground crew indicators in the cockpit. HiPC-A will process and distribute commands from the cockpit to the six HLMC on the A system and HiPC-B will process and distribute commands from the cockpit to six HLMCs on the B system.

The cockpit provides commands to the HiPC using an Arm/Disarm switch that arms and disarms the HLMCs and a Mode switch that places the HLMCs in an Airspeed or Fixed Control Mode. The Airspeed Mode varies motor RPM with Airspeed. The Fixed Mode commands the motor to a fixed or constant RPM. There is also a yoke mounted disarm switch which allows the pilot to quickly disarm the HLMCs. If the yoke mounted disarm switch is engaged by the pilot, the HLMCs will disarm and stay disarmed. An indicator will notify the pilot that the HLMCs are disarmed but the Arm/Disarm switch is still in the Arm position. This indicator will turn off when the pilot places the Arm/Disarm switch in the Disarm position.

HiPC-A, HiPC-B, HiPI-A and HiPI-B will each have an independent circuit breaker in the cockpit providing power. This will isolate the power to each unit and prevent a power fault in one unit causing a power fault in the remaining units.

# 2.1 System Diagram

High Lift Motor and High Lift Motor Controller distribution across the Mod III/IV wing is shown in Figure 1

Figure 1 – High Lift Propulsor Distribution

#### A functional block diagram and interfaces for HiPI and HiPC is shown in Figure 2

Figure 2 – HiPI & HiPC Block Diagram with Interfaces

# **3** Applicable Documents

The following documents were used to assist in the development of the requirements specified in this document

- a. ETP-CEPT-007, Environmental Test Plan

- b. REQ-CEPT-018, High lift Motor Controller Hardware Requirements Document

- c. QAP-CEPT-008, Quality Assurance Plan

- d. ANLYS-CEPT-023, Analysis of X-57 High lift Propeller Operating Conditions

- e. ANLYS-CEPT-032, Mod IV Avionics Power Analysis

- f. ICD-CEPT-006, Cockpit ICD

## **4** Requirements Standards

The following format was used to develop the requirements.

- Requirements are in the form "who shall do what".

- Requirements use the proper terminology:

- o "Shall" is used to denote a binding requirement.

- "Will" is a statement of fact or declaration of purpose.

- o "Should" is used to denote an optional goal.

- Requirements are clear, concise, and unambiguous.

- Requirements are verifiable through inspection, analysis, test, or demonstration.

- Rationale is provided as a means to capture the purpose of the requirement. Its intent is to aid the reader in understanding the requirements. The rationale does not contain any requirements; therefore, no verification of the rationale is required.

### **5** Requirements Verification Methods

Requirement verification methods are not under configuration control, and may be changed by the requirement owner, with agreement from the associated IPT. The actual verification method used to close a requirement is documented in the requirements verification sheet.

The requirement verification methods employed are inspection, analysis, test, and demonstration. The following sections define the verification methods used.

#### 5.1 Verification Method - Inspection

Inspections determine conformance to requirements by the visual examination of drawings, data, or the item itself using standard quality control methods, without the use of special laboratory procedures or equipment. Inspection includes examining a direct physical attribute such as dimension, weight, physical characteristics, color or markings.

#### 5.2 Verification Method - Analysis

Analysis is the evaluation of data by generally accepted analytical techniques to determine that the item will meet specified requirements. Analysis is selected as the verification activity when test or demonstration techniques cannot adequately or cost effectively address all the conditions under which the system must perform, or the system cannot be shown to meet the requirement without analysis.

#### 5.3 Verification Method - Test

Test is a verification method in which technical means, such as the use of special equipment, instrumentation, simulation techniques, or the application of established principles and procedures are used for the evaluation of the system or system components to determine compliance with requirements. Test consists of operation of all or part of the system under a limited set of controlled conditions to determine the quantitative design or performance requirements have been met. Tests may rely on the use of elaborate instrumentation and special test equipment to measure the parameters that characterize the requirements.

The analysis of data derived from tests is an integral part of the test program and should not be confused with "analysis" as defined earlier. Testing is the preferred method of verification when:

- Analytical techniques do not produce adequate results

- Failure modes exist which could compromise personnel safety, adversely affect flight systems or result in a loss of mission objective

- Components are directly associated with critical system interfaces

#### **5.4 Verification Method - Demonstration**

Verification by demonstration shows that an end product meets the performance or operational requirement in a qualitative manner. It is used for determination of properties of an end item or component by observation of its operation or characteristics. It is generally a basic confirmation of performance capability, differentiated from testing by the lack of detailed data gathering.

# 6 High Lift Propeller Control (HiPC) Requirements

#### **6.1 HiPC Interface Requirements**

These requirements apply to HiPC-A and HiPC-B. Please refer to **Figure 2** for the HiPC-A and HiPC-B interface boundaries

| Req. #     | Requirement                                                                                                                                                      | Rationale                                                                                                                                                                                       | Verification<br>Method | Requirements<br>Trace | Safety<br>Critical                                             |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------|----------------------------------------------------------------|

|            |                                                                                                                                                                  | HiPC ARM Command                                                                                                                                                                                |                        |                       |                                                                |

| HIPC.1     | The HiPC shall provide an Arm signal<br>to the HLMCs when the<br>ARM/DISARM switch in the cockpit is<br>moved from the DISARM position to<br>the ARM position.   | A pilot selectable switch is used to<br>Arm and Disarm the High Lift<br>System.                                                                                                                 | Demonstration          | C.3.1.1               | HR-30 Cause<br>H, HR-31<br>Cause R<br>HR-31 Cause<br>R, Mit 31 |

| HIPC.1.1   | The HiPC Arm signal from the<br>ARM/DISARM switch in the cockpit<br>shall be a closed circuit.                                                                   | A closed circuit will prevent the<br>accidental arming of the HLMC by<br>an open circuit caused by a broken<br>wire or unmated connector.<br>Disarm is the failsafe condition for<br>the HLMCs. | Test                   | HIPC.1                | See HIPC.1                                                     |

| HIPC.1.1.1 | The HiPC Arm closed circuit from the ARM/DISARM switch in the cockpit shall have a resistance of less than 10 $\Omega$ as measured at the Arm input to the HiPC. | 10 $\Omega$ of resistance is adequate<br>resistance to indicate a closed<br>circuit. This would include wire<br>resistance, connector resistance<br>switch closure resistance plus<br>margin.   | Test                   | HIPC.1.1              | See HIPC.1                                                     |

| HIPC.1.2   | The HiPC Arm voltage output signal<br>provided to the HLMC shall reference<br>the HiPC power return                                                              | The LCA715STR opto-isolator in the HLMC is a single ended device and does not accept a differential signal.                                                                                     | Test                   | HIPC.1                | See HIPC.1                                                     |

| Req. #       | Requirement                                                                                                                                                      | Rationale                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Verification<br>Method | Requirements<br>Trace | Safety<br>Critical                                                       |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------|--------------------------------------------------------------------------|

| HIPC.1.2.1   | The HiPC Arm voltage output signal<br>provided to the HLMC shall range<br>between 14 VDC to 16 VDC                                                               | A voltage must be applied to the<br>HLMC input to Arm the motors and<br>start the motors spinning. This will<br>prevent the motors from spinning<br>due to a loss of voltage.<br>The HLMC has 630 ohms in series<br>with the LCA715STR opto-isolator<br>LED to activate the ARM<br>command. 14 VDC will continually<br>source 20.3ma into the LED. 16<br>VDC will continually source<br>23.5ma. The minimum current<br>required to activate the opto-<br>isolator LED is 1ma to 5ma. Peak<br>current is 50ma continuous or<br>1 amp for 10ms. 20 to 25ma will<br>provided a robust signal to activate | Test                   | HIPC.1.2              | See HIPC.1                                                               |

|              | The HIPC Arm signal shall have a                                                                                                                                 | the LED for the ARM command.<br>The output current must below the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>T</b> = = #         |                       |                                                                          |

| HIPC.1.2.1.1 | current limit of 30 ma                                                                                                                                           | peak input current for the<br>LCA715STR opto-isolator LED.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Test                   | HIPC.1.2.1            | See HIPC.1                                                               |

|              |                                                                                                                                                                  | HiPC DISARM Command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | r                      |                       | o state addre dat in state                                               |

| HIPC.2       | The HiPC shall provide a Disarm<br>signal to the HLMCs when the<br>ARM/DISARM switch in the cockpit is<br>moved from the ARM position to the<br>DISARM position. | A pilot selectable switch is used to<br>Arm and Disarm the High Lift<br>System.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Demonstration          | C.3.1.4               | HR-30.2 Mit.<br>8<br>HR-30.1 Mit.<br>13, HR-30<br>Cause H, J,<br>Mit. 13 |

| HIPC.2.1     | The HiPC Disarm signal from the<br>ARM/DISARM switch in the cockpit<br>shall be an open circuit.                                                                 | The default condition for the HLMC<br>is Disarm. An open circuit caused<br>by a broken wire or an unmated<br>connector will default the HLMC to<br>the Disarm. This is a "fail safe"<br>condition.                                                                                                                                                                                                                                                                                                                                                                                                    | Test                   | HIPC.2                | See HIPC.2                                                               |

| Req. #     | Requirement                                                                                                                                                                                                                                   | Rationale                                                                                                                                                                                                                                      | Verification<br>Method | Requirements<br>Trace | Safety<br>Critical |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------|--------------------|

| HIPC.2.1.1 | The HiPC Disarm open circuit from<br>the ARM/DISARM switch in the<br>cockpit shall have a resistance of at<br>least 100k $\Omega$ as measured at the<br>Disarm input to the HiPC.                                                             | More than 100k $\Omega$ of resistance is adequate to indicate an open circuit.                                                                                                                                                                 | Test                   | HIPC.2.1              | See HIPC.2         |

| HIPC.2.2   | The HiPC Disarm signal provided to the HLMC shall be a voltage referenced to the HiPC power return.                                                                                                                                           | The LCA715STR opto-isolator in<br>the HLMC is a single ended device<br>and does not accept a differential<br>signal.                                                                                                                           | Test                   | HiPC.2                | See HIPC.2         |

| HIPC.2.2.1 | The HiPC Disarm signal voltage to the HLMC shall be less than 1.6 VDC.                                                                                                                                                                        | 0 VDC will replicate an open wire<br>or loss of voltage and will cause<br>the HLMC to disarm. This is a "fail<br>safe" condition. Voltage limit<br>provided by HLMC engineer at<br>GRC.                                                        | Test                   | HiPC.2.2              | See HIPC.2         |

|            |                                                                                                                                                                                                                                               | Yoke DISARM Command                                                                                                                                                                                                                            |                        |                       |                    |

| HIPC.2.3   | The HiPC shall provide a Disarm<br>signal to the HLMCs when both of the<br>conditions below are satisfied:<br>1. The Yoke DISARM switch in the<br>cockpit is engaged AND<br>2. The ARM/DISARM switch in the<br>cockpit is in the ARM position | A yoke mounted disarm switch will<br>allow the pilot to quickly disarm the<br>HLMC while using only his left<br>thumb.<br>This is the same functionality as<br>flipping the instrumented panel<br>ARM/DISARM switch to the<br>Disarm position. | Demonstration          | HIPC.2                | See HIPC.2         |

| HIPC.2.3.1 | The HiPC Disarm signal from the<br>Yoke Disarm switch in the cockpit<br>shall provide a momentary open<br>circuit for at least 0.010 ms.                                                                                                      | The yoke disarm switch is a spring<br>loaded push button switch. The<br>switch is normally closed and will<br>provided momentary open circuit<br>when engaged by the pilot before<br>returning to the normally closed<br>position.             | Test                   | HIPC.2.3              | See HIPC.2         |

| Req. #       | Requirement                                                                                                                                                                         | Rationale                                                                                                                                                                                                                                                            | Verification<br>Method | Requirements<br>Trace | Safety<br>Critical                                           |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------|--------------------------------------------------------------|

| HIPC.2.3.1.1 | The HiPC Disarm open circuit from<br>the Yoke Disarm switch in the cockpit<br>shall have a resistance of at least<br>100k $\Omega$ as measured at the Disarm<br>input to the HiPC.  | More than 100k $\Omega$ of resistance is adequate to indicate an open circuit.                                                                                                                                                                                       | Test                   | HIPC.2.3.1            | See HIPC.2                                                   |

| HIPC.2.3.2   | The HiPC shall continue to assert the<br>Disarm signal initiated by the Yoke<br>Disarm switch to the HLMCs until a<br>reset is issued by the instrument<br>panel ARM/DISARM switch. | The yoke mounted disarm switch<br>is intended to quickly Disarm the<br>HLMC, and latch the Disarm<br>signal, until a reset is initiated by<br>the ARM/DISARM switch.                                                                                                 | Test                   | HIPC.2.3              | See HIPC.2                                                   |

| HIPC.2.3.2.1 | The HiPC shall issue a Disarm Reset<br>when the cockpit ARM/DISARM<br>switch is placed to the DISARM<br>position.                                                                   | This resets the Yoke disarm<br>command and allows for the pilot<br>to resume normal HLMC<br>operations.                                                                                                                                                              | Test                   | HIPC.2.3.2            | See HIPC.2                                                   |

| HIPC.2.3.2.2 | The HiPC system shall detect when<br>the Yoke Disarm switch has opened<br>the Arm circuit but the instrument<br>panel ARM/DISARM switch is still in<br>the ARM position.            | The HiPC needs to detect a switch<br>mismatch to indicate the mismatch<br>switch status to the cockpit. The<br>expected response in the cockpit<br>is defined in requirement<br>HIPC.6.5.                                                                            | Test                   | HIPC.2.3.2            | See HIPC.2                                                   |

|              |                                                                                                                                                                                     | Airspeed Mode                                                                                                                                                                                                                                                        |                        |                       | ×                                                            |

| HIPC.3       | The HiPC shall provide an Airspeed<br>Mode signal to the HLMCs when the<br>AIRSPEED/FIXED switch in the<br>cockpit is placed in the AIRSPEED<br>position.                           | A pilot selectable switch is used to<br>place the HLMC in an Airspeed<br>Mode or a Fixed Mode. In the<br>Airspeed Mode, the HLMC<br>commands a motor RPM based on<br>an airspeed schedule. In the<br>Fixed Mode, the HLMC commands<br>a fixed motor RPM of 4800 RPM. | Demonstration          | C.6.1.3               | HR-30.1<br>Cause C<br>Mit 15<br>HR-30Cause<br>I, K<br>Mit 15 |

| HIPC.3.1     | The HiPC Airspeed mode signal from<br>the AIRSPEED/FIXED switch in the<br>cockpit shall be a closed circuit.                                                                        | A closed circuit will prevent the<br>HLMC accidently going into the<br>airspeed mode due to open circuit<br>caused by a broken wire or<br>unmated connector. Fixed Mode<br>is the failsafe condition for the<br>HLMC.                                                | Test                   | HiPC.3                | See HIPC.3                                                   |

| Req. #       | Requirement                                                                                                                                                                         | Rationale                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Verification<br>Method | Requirements<br>Trace | Safety<br>Critical |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------|--------------------|

| HIPC.3.1.1   | The HiPC Airspeed mode closed circuit from the AIRSPEED/FIXED switch in the cockpit shall have a resistance of less than $10 \Omega$ as measured at the Airspeed input to the HiPC. | 10 $\Omega$ of resistance is adequate resistance to indicate a closed circuit. This would include wire resistance, connector resistance switch closure resistance plus margin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Test                   | HIPC.3.1              | See HIPC.3         |

| HIPC.3.2     | The HiPC Airspeed Mode voltage<br>output signal provided to the HLMC<br>shall reference the HiPC power return                                                                       | The LCA715STR opto-isolator in<br>the HLMC is a single ended device<br>and does not accept a differential<br>signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Test                   | HIPC.3                | See HIPC.3         |

| HIPC.3.2.1   | The HiPC Airspeed Mode voltage<br>output signal provided to the HLMC<br>shall range between 14 VDC to 16<br>VDC                                                                     | A voltage must be applied to the<br>HLMC input to place the motors in<br>the Airspeed Mode. This will<br>prevent the HLMC from defaulting<br>to the airspeed mode due to a loss<br>of voltage.<br>The HLMC has 630 ohms in series<br>with the LCA715STR opto-isolator<br>LED to activate the Airspeed Mode<br>command. 14 VDC will continually<br>source 20.3ma into the LED. 16<br>VDC will continually source<br>23.5ma. The minimum current<br>required to activate the opto-<br>isolator LED is 1ma to 5ma. Peak<br>current is 50ma continuous or<br>1 amp for 10ms. 20 to 25ma will<br>provided a robust signal to activate<br>the LED for the Airspeed Mode<br>command. | Test                   | HIPC.3.2              | See HIPC.3         |

| HIPC.3.2.1.1 | The HIPC Airspeed Mode signal shall have a current limit of 30 ma                                                                                                                   | The output current must below the<br>peak input current for the<br>LCA715STR opto-isolator LED.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Test                   | HIPC.3.2.1            | See HIPC.3         |

| Req. #     | Requirement                                                                                                                                                                            | Rationale                                                                                                                                                                                                                                                            | Verification<br>Method | Requirements<br>Trace | Safety<br>Critical                                            |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------|---------------------------------------------------------------|

|            |                                                                                                                                                                                        | Fixed Mode                                                                                                                                                                                                                                                           |                        |                       |                                                               |

| HIPC.4     | The HiPC shall provide a Fixed Mode<br>signal to the HLMCs when the<br>AIRSPEED/FIXED switch in the<br>cockpit is placed in the FIXED<br>position.                                     | A pilot selectable switch is used to<br>place the HLMC in an Airspeed<br>Mode or a Fixed Mode. In the<br>Airspeed Mode, the HLMC<br>commands a motor RPM based on<br>an airspeed schedule. In the<br>Fixed Mode, the HLMC commands<br>a fixed motor RPM of 4800 RPM. | Demonstration          | C.6.1.3               | HR-30.1<br>Cause C<br>Mit 15<br>HR-30 Cause<br>I, K<br>Mit 15 |

| HIPC.4.1   | The HiPC Fixed Mode signal from the<br>AIRSPEED/FIXED switch in the<br>cockpit shall be an open circuit.                                                                               | The default condition for the HLMC<br>is Disarm. An open circuit caused<br>by a broken wire or an unmated<br>connector will default the HLMC to<br>the Disarm. This is a "fail safe"<br>condition.                                                                   | Test                   | HIPC.4                | See HIPC.4                                                    |

| HIPC.4.1.1 | The HiPC Fixed Mode open circuit<br>from the AIRSPEED/FIXED switch in<br>the cockpit shall have a resistance of<br>at least 100k $\Omega$ as measured at the<br>Arm input to the HiPC. | More than 100k $\Omega$ of resistance is adequate to indicate an open circuit.                                                                                                                                                                                       | Test                   | HIPC.4.1              | See HIPC.4                                                    |

| HIPC.4.2   | The HiPC Fixed Mode signal<br>provided to the HLMC shall be a<br>voltage referenced to the HiPC power<br>return.                                                                       | The LCA715STR opto-isolator in the HLMC is a single ended device and does not accept a differential signal.                                                                                                                                                          | Test                   | HiPC.4                | See HIPC.4                                                    |

| HIPC.4.2.1 | The HiPC Fixed Mode signal voltage<br>to the HLMC shall be less than 1.6<br>VDC.                                                                                                       | 0 VDC will replicate an open wire<br>or loss of voltage and will cause<br>the HLMC to disarm. This is a "fail<br>safe" condition. Voltage limit<br>provided by HLMC engineer at<br>GRC.                                                                              | Test                   | HiPC.4.2              | See HIPC.4                                                    |

| Req. #   | Requirement                                                                              | Rationale                                                                                                                                                                                                                                                                                                                                 | Verification<br>Method | Requirements<br>Trace | Safety<br>Critical                 |

|----------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------|------------------------------------|

|          |                                                                                          | A/B Architecture                                                                                                                                                                                                                                                                                                                          |                        |                       |                                    |

| HIPC.5   | The HiPC shall conform to the A/B system architecture define in <b>Figure 2</b> .        | The A and B high lift propulsors<br>are distributed across the left and<br>right wing so that a failure of an A<br>system or a B system will not<br>produce an abrupt asymmetric<br>thrust event and cause an adverse<br>yaw condition for the aircraft. See<br><b>Figure 1</b> for the high lift propulsors<br>distribution on the wing. | Inspection             | V26.1<br>P24.2        | HR-30 Cause<br>C, I and L<br>Mit 4 |

| HIPC.5.1 | HiPC-A shall provide command<br>signals to HLMCs at locations 1, 3, 5,<br>8, 10, and 12. | A failure of HiPC-A system or<br>HiPC-B will not produce an abrupt<br>asymmetric thrust event and cause<br>an adverse yaw condition for the<br>aircraft.                                                                                                                                                                                  | Demonstration          | HIPI.5                | See HIPC.5                         |

| HIPC.5.2 | HiPC-B shall provide command<br>signals to HLMCs at locations 2, 4, 6,<br>7, 9, and 11.  | A failure of HiPC-A system or<br>HiPC-B will not produce an abrupt<br>asymmetric thrust event and cause<br>an adverse yaw condition for the<br>aircraft.                                                                                                                                                                                  | Demonstration          | HIPI.5                | See HIPC.5                         |

### 6.2 HiPC Cockpit Requirements

These requirements apply to the cockpit switches and indicators that interface to the HiPC-A and HiPC-B. Please refer to **Figure 2** for the cockpit interface boundaries

| Req. #     | Requirement                                                                                                                           | Rationale                                                                     | Verification<br>Method | Requirements<br>Trace | Safety<br>Critical                                                       |

|------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------|-----------------------|--------------------------------------------------------------------------|

|            |                                                                                                                                       | HiPC                                                                          |                        | •                     |                                                                          |

| HIPC.6     | The HiPC switches and indicators<br>shall follow the layout configuration<br>as defined in the Cockpit ICD (ICD-<br>CEPT-006).        | The cockpit layout is defined in the Cockpit ICD (ICD-CEPT-006).              | Inspection             | V5.2                  | HR30                                                                     |

| HIPC.6.1   | The HiPI switches and indicator<br>labeling shall meet the<br>requirements defined in MIL-STD-<br>1472H, section 5.4.2 through 5.4.3. | MIL-STD-1472H dictates this as a<br>Human Systems Integration<br>Requirement. | Inspection             | HIPC.6                | See HIPI.6                                                               |

| HIPC.6.2   | The HIPC Yoke Disarm switch shall reside on the cockpit yoke.                                                                         | A yoke switch allows for quick<br>Disarming of the HL system.                 | Inspection             | C3.1.4                | HR-30.2 Mit.<br>8<br>HR-30.1 Mit.<br>13, HR-30<br>Cause H, J,<br>Mit. 13 |

| HIPC.6.2.1 | The HiPC Yoke Disarm switch<br>shall use a momentary style of<br>switch.                                                              | A momentary switch is located on the Yoke to quickly disarm the system.       | Inspection             | HIPC.6.2              | See HIPC.6.2                                                             |

| HIPC.6.3   | The HIPC ARM/DISARM switch<br>shall reside on the instrument<br>panel.                                                                | The cockpit layout is defined in the Cockpit ICD (ICD-CEPT-006).              | Inspection             | C3.1.1<br>C3.1.4      | See HIPC.6.2                                                             |

| HIPC.6.3.1 | The HIPC ARM/DISARM switch<br>shall ARM and DISARM the high<br>lift system.                                                           | A switch is needed to close or open the Arm circuit.                          | Inspection             | HIPC.6.3              | See HIPC.6.2                                                             |

| HIPC.6.4   | The HIPC Mode Control select<br>switch shall reside on the<br>instrument panel.                                                       | The cockpit layout is defined in the Cockpit ICD (ICD-CEPT-006).              | Inspection             | V3.1.7<br>V6.1        | See HIPC.6.2                                                             |

| Req. #       | Requirement                                                                                                                                                              | Rationale                                                                                                                                                                                  | Verification<br>Method | Requirements<br>Trace | Safety<br>Critical                                              |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------|-----------------------------------------------------------------|

| HIPC.6.4.1   | The HIPC Mode Select switch shall<br>select Fixed or Airspeed mode<br>operations.                                                                                        | The HL system has two modes of control, Fixed and Airspeed.                                                                                                                                | Inspection             | HIPC.6.4              | HR-30.1<br>Cause C<br>Mit 15<br>HR-30.2<br>Cause I, K<br>Mit 15 |

| HIPC.6.5     | The HiPC system shall send an<br>electrical output to the Reset<br>Required indicator when a switch<br>mismatch is detected as described<br>in Requirement HIPC.2.3.2.2. | Quickly alerts the pilot the Yoke<br>Disarm switch was engaged to<br>Disarm the HL system instead of the<br>Arm/Disarm Switch.                                                             | Test                   | C3.1.4<br>P.26.1.1    | See HIPC.6.2                                                    |

| HIPC.6.5.1   | The HiPC system Reset Required<br>indicator shall reside on the<br>instrument panel.                                                                                     | The cockpit layout is defined in the Cockpit ICD (ICD-CEPT-006).                                                                                                                           | Inspection             | HIPI.6.3              | See HIPC.6.2                                                    |

| HIPC.6.5.2   | The HiPC Reset Required indicator<br>shall be sunlight-readable in<br>accordance with luminance criteria<br>in MIL-STD-1472H, 5.2.3.3.3.1<br>through 5.2.3.3.3.4.        | Ensures indicators are readable in the flight environment.                                                                                                                                 | Demonstration          | HIPI.6.5              | See HIPC.6.2                                                    |

| HiPC.6.5.3   | The HiPC shall receive a signal<br>from the X-57 Cockpit Light Check<br>switch to illuminate the HiPC Reset<br>Required indicator.                                       | One switch in the cockpit verifies all<br>cockpit indicators turn on and<br>illuminate. This is performed as part<br>of a preflight test.                                                  | Demonstration          | HIPI.6.5              | See HIPC.6.2                                                    |

| HiPC.6.5.3.1 | The HiPC signal received from the X-57 Cockpit Light Check switch shall be a closed circuit.                                                                             | The X-57 Cockpit Light Check switch<br>is a "Push to Test" switch is normally<br>open and closes when engaged by<br>the pilot.                                                             | Demonstration          | HIPI.6.5.3            | See HIPC.6.2                                                    |

| HiPC.6.5.3.2 | The HiPC closed circuit resistance<br>received from X-57 Cockpit Light<br>Check switch shall be less than 10<br>$\Omega$ as measured at the input to the<br>HiPC.        | 10 $\Omega$ of resistance is adequate<br>resistance to indicate a closed circuit.<br>This would include wire resistance,<br>connector resistance switch closure<br>resistance plus margin. | Test                   | HIPI.6.5.3            | See HIPC.6.2                                                    |

# 7 High Lift Propeller Indicator (HiPI) Requirements

#### 7.1 HiPI Interface Requirements

These requirements apply to HiPI-A and HiPI-B. Please refer to Figure 2 for the HiPI-A and HiPI-B interface boundaries

| Req. #     | Requirement                                                                                                                 | Rationale                                                                                                                                                                                                                        | Verification<br>Method | Requirements<br>Trace | Safety<br>Critical                     |

|------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------|----------------------------------------|

|            | ·*                                                                                                                          | HiPI Cockpit Interface                                                                                                                                                                                                           |                        |                       |                                        |

| HIPI.1     | The HiPI shall report the status of the HLMC to the cockpit.                                                                | The HiPI is the interface between<br>the HLMCs and the cockpit status<br>indicators for the High Lift System.                                                                                                                    | Inspection             | C.2.3.3               | HR-30 Cause<br>A, C, H, I, K<br>Mit. 6 |

| HIPI.1.1   | The HiPI shall provide electrical<br>outputs to illuminate the Pilot<br>Cockpit Status Indicators.                          | The Pilot Indicators will provide the<br>HL system status during flight<br>operations.                                                                                                                                           | Inspection             | HIPI.1                | See HIPI.1                             |

| HIPI.1.1.1 | The HiPI shall illuminate the Pilot<br>Cockpit Status Indicators as defined<br>in <b>Table 1</b> .                          | The Cockpit Pilot Indicators report<br>a combined status for the HL<br>system status based on the status<br>of multiple HLMCs. The display is<br>simple so the pilot can quickly<br>asses the status of the high lift<br>system. | Test                   | HIPI.1.1              | See HIPI.1                             |

| HIPI.1.1.2 | The HiPI shall illuminate the Pilot<br>Cockpit Status Indicators based on<br>the priority logic defined in <b>Table 1</b> . | To simplify the amount of<br>information available to the Pilot, a<br>priority must be assigned to each<br>indicator.                                                                                                            | Test                   | HIPI.1.1              | See HIPI.1                             |

| HIPI.1.2   | The HiPI shall provide electrical<br>outputs to illuminate the Cockpit<br>Ground Crew Indicators.                           | The Ground Crew Cockpit Status<br>Indicators will provide the HL<br>system status during ground<br>operations, including system<br>testing.                                                                                      | Inspection             | HIPI.1                | See HIPI.1                             |

| HIPI.1.2.1 | The HiPI system shall illuminate the Ground Crew Cockpit Status Indicators as defined in <b>Table 2</b> .                   | The Ground Crew Cockpit Status<br>Indicators reports the status of<br>each HLMC. This will allow the<br>ground crew quickly identify the<br>status of each HLMC.                                                                 | Test                   | HIPI.1.2              | See HIPI.1                             |

| Req. #              | Requirement                                                                                                                                           | Rationale                                                                                                                                                                                     | Verification<br>Method | Requirements<br>Trace | Safety<br>Critical                    |  |  |  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------|---------------------------------------|--|--|--|

| HiPI HLMC Interface |                                                                                                                                                       |                                                                                                                                                                                               |                        |                       |                                       |  |  |  |

| HIPI.2              | The HiPI shall receive four HLMC discrete status signals from each HLMC.                                                                              | The four discrete signal will provide the status for each HLMC.                                                                                                                               | Inspection             | C2.3.3                | HR30 Cause<br>A, C, H, I, K<br>Mit. 6 |  |  |  |

| HIPI.2.1            | The HiPI discrete status signal<br>received from the HLMC shall be an<br>open circuit to represent a low level<br>logic state.                        | An open circuit (off) represents a<br>Logic Level 0.                                                                                                                                          | Test                   | HIPI.2                | See HIPI.2                            |  |  |  |

| HIPI.2.1.1          | The HiPI discrete status signal open circuit resistance received from the HLMC shall be at least $100k \Omega$ as measured at the input to the HiPI.  | More than 100k $\Omega$ of resistance is adequate to indicate an open circuit.                                                                                                                | Test                   | HIPI.2                | See HIPI.2                            |  |  |  |

| HIPI.2.2            | The HiPI discrete status signal received from the HLMC shall be a closed circuit to represent a high level logic state.                               | A closed circuit (on) represents a<br>Logic Level 1.                                                                                                                                          | Test                   | HIPI.2                | See HIPI.2                            |  |  |  |

| HIPI.2.2.1          | The HiPI discrete status signal closed circuit resistance received from the HLMC shall be less than 10 $\Omega$ as measured at the input to the HiPI. | 10 $\Omega$ of resistance is adequate<br>resistance to indicate a closed<br>circuit. This would include wire<br>resistance, connector resistance<br>switch closure resistance plus<br>margin. | Test                   | HIPI.2                | See HIPI.2                            |  |  |  |

| HIPI.2.3            | The HiPI discrete status signals<br>shall be labeled GPIO 10, GPIO 11,<br>GPIO 12 and GPIO 13.                                                        | Provides HLMC signal labels for<br>cockpit displays logic table.                                                                                                                              | Inspection             | HIPI.2                | See HIPI.2                            |  |  |  |

| HIPI.2.4            | The HiPI system shall electrically<br>isolate the HLMC GPIO signals from<br>the HiPC signal conditioning.                                             | Signal isolation is required to preserve signal integrity.                                                                                                                                    | Test                   | C.1.1.3               | HR-19B<br>Cause C, Mit.<br>4          |  |  |  |

|                     |                                                                                                                                                       | A/B Architecture                                                                                                                                                                              |                        | *<br>*                | 5)<br>7)                              |  |  |  |

| HIPI.3              | The HiPI system shall consist of two<br>identical, independent systems<br>labeled Side A and Side B.                                                  | The HiPI architecture should<br>match existing aircraft<br>architectures.                                                                                                                     | Inspection             | V26.1<br>P24.2        | HR-30 Cause<br>C, I and L<br>Mit. 4   |  |  |  |

| HIPI.3.1            | HiPI-A shall process status signals<br>from HLMCs at locations 1, 3, 5, 8,<br>10, and 12.                                                             | Side A of other vehicle systems,<br>such as avionics and traction<br>power distribution systems, is<br>defined as listed.                                                                     | Demonstration          | HIPI.3                | See HIPI.3                            |  |  |  |

| Req. #   | Requirement                                                                              | Rationale                                                                                                                 | Verification<br>Method | Requirements<br>Trace | Safety<br>Critical |

|----------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------|--------------------|

| HIPI.3.2 | HiPI-B shall process status signals<br>from HLMCs at locations 2, 4, 6, 7,<br>9, and 11. | Side B of other vehicle systems,<br>such as avionics and traction<br>power distribution systems, is<br>defined as listed. | Demonstration          | HIPI.3                | See HIPI.3         |

| HIPI.3.3 | The HiPl electrical output shall use discrete logic.                                     | Simple architectures should be<br>used where possible. Simplifies<br>control and design validation.                       | Inspection             | HIPI.3                | See HIPI.3         |

| Priority | Rule                                                | HLMC GPIO<br>(10-11-12-13) | Status |

|----------|-----------------------------------------------------|----------------------------|--------|

|          | Indicator 1                                         |                            | *      |

| 1        | If all 'Ready'                                      | 0-1-0-0                    |        |

| 2        | If all 'Airspeed Run'                               | 1-0-0-1                    | •      |

|          |                                                     | 1-1-0-1                    |        |

| 3        | If any 'Maintenance'                                | 1-1-1-0                    |        |

|          |                                                     | 1-1-1-1                    |        |

| 4        | If any 'Init'                                       | 0-0-0-1                    | 0      |

| 5        | If any 'Waiting'                                    | 0-0-1-1                    | 0      |

| 6        | If any 'Airspeed Default Run'                       | 1-0-1-0                    | 0      |

| 7        | If any 'Ready'                                      | 0-1-0-0                    |        |

| 8        | If any 'Airspeed Run'                               | 1-0-0-1                    | 0      |

| 9        | Else                                                |                            | 0      |

|          | Indicator 2                                         |                            |        |

| 1        | If all 'Fixed Run'                                  | 1-0-0-0                    |        |

| 2        | If all 'Airspeed Run'                               | 1-0-0-1                    |        |

| 3        |                                                     | 1-1-0-1                    | Page 1 |

|          | If any 'Maintenance'                                | 1-1-1-0                    |        |

| 619      | ean taisear anna an an an ann an Anna ann ann ann a | 1-1-1-1                    |        |

| 4        | If any 'Spin Up'                                    | 0-1-1-1                    | 0      |

| 5        | If any 'Spin Down'                                  | 0-1-1-1                    | 0      |

| 6        | If any 'Airspeed Default Run'                       | 1-0-0-1                    | 0      |

| 7        | If any 'Fixed Run'                                  | 1-0-0-0                    |        |

| 8        | If any 'Airspeed Run'                               | 1-0-0-1                    | •      |

| 9        | Else                                                |                            | 0      |

| The day  | Indicator 3                                         |                            |        |

|          |                                                     | 1-1-0-1                    |        |

| 1        | If any 'Maintenance'                                | 1-1-1-0                    |        |

|          | 8                                                   | 1-1-1-1                    |        |

| 2        | If any 'Armed Fault'                                | 1-0-1-1                    | 0      |

| 3        | If any 'HV Fault'                                   | 0-1-1-0                    |        |

| 4        | If any 'Air Data Fault'                             | 0-1-0-1                    |        |

| 5        | If any 'Terminal Fault'                             | 1-1-0-0                    | •      |

| 6        | If any 'PUBiT Fault'                                | 0-0-1-0                    |        |

| 7        | Else                                                |                            | 0      |

#### Table 1 – Pilot Cockpit Status Indicators ○ Indicator Off, ● Indicator On, ● Indicator Flashing

|                          | round Crew Cockpit I           | ndicators                                  |

|--------------------------|--------------------------------|--------------------------------------------|

| HLMC GPIO<br>10-11-12-13 | Ground Crew<br>Indicator (x12) | HLMC Condition                             |

| 0-0-0                    | 000                            | Off                                        |

| 0-0-0-1                  | • • •                          | Initializing                               |

| 0-0-1-0                  |                                | PUBiT Fault                                |

| 0-0-1-1                  | 00                             | Waiting                                    |

| 0-1-0-0                  | 000                            | Ready                                      |

| 0-1-0-1                  | 00                             | Air Data Fault                             |

| 0-1-1-0                  | 00                             | HV Fault                                   |

| 0-1-1-1                  | 000                            | Spin Up<br>Spin Down<br>Maintenance - Test |

| 1-0-0-0                  | 000                            | Fixed Run                                  |

| 1-0-0-1                  |                                | Airspeed Run                               |

| 1-0-1-0                  | 00                             | Airspeed Default Run                       |

| 1-0-1-1                  | 000                            | Armed Fault                                |

| 1-1-0-0                  | 00●                            | Terminal Fault                             |

| 1-1-0-1                  |                                | Maintenance - Load                         |

| 1-1-1-0                  |                                | Maintenance - Ready                        |

| 1-1-1-1                  | 0 🕚 🔴                          | Maintenance - Fault                        |

# Table 2 – Ground Crew Cockpit Status Indicators O Indicator Off Indicator Off

#### 7.2 HiPI Cockpit Status Indicator Requirements

These requirements apply to the cockpit indicators that interface to the HiPI-A and HiPI-B. Please refer to **Figure 2** for the cockpit interface boundaries

| Req. #       | Requirement                                                                                                                                                        | Rationale                                                                                                                                          | Verification<br>Method | Requirements<br>Trace | Safety<br>Critical                    |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------|---------------------------------------|

| HIPI.5       | The HIPI system cockpit status<br>indicators shall reside on the cockpit<br>instrument panel.                                                                      | The cockpit layout is defined in the Cockpit ICD (ICD-CEPT-006).                                                                                   | Inspection             | V5.2<br>C2.3.3        | HR30 Cause<br>A, C, H, I, K<br>Mit. 6 |

| HIPI.5.1     | The HiPl cockpit status indicator's<br>flash rate shall be no greater than 5<br>Hz and no less than 0.8 Hz.                                                        | MIL-STD-1472H 5.17.27.3.3<br>dictates this as a Human Systems<br>Integration Requirement.                                                          | Demonstration          | HIPI.5                | See HIPI.5                            |

| HIPI.5.1.1   | The HiPI cockpit status indicator's<br>flash rate duty cycle percentage of<br>"on" time shall be equal to but not<br>less than the percentage of "off" time.       | MIL-STD-1472H 5.17.27.2<br>dictates this as a Human Systems<br>Integration Requirement. A 50<br>percent duty cycle is preferred.                   | Demonstration          | HIPI.5.1              | See HIPI.5                            |

| HIPI.5.2     | The HiPI flashing cockpit status<br>indicator's <del>flash s</del> hall be<br>synchronized.                                                                        | FAA AC 25.1322-1 dictates this as<br>Human Systems Integration<br>Requirement.                                                                     | Demonstration          | HIPI.5                | See HIPI.5                            |

| HIPI.5.3     | The HiPI cockpit status indicators<br>shall be sunlight-readable in<br>accordance with luminance criteria in<br>MIL-STD-1472H, 5.2.3.3.3.1 through<br>5.2.3.3.3.4. | Ensures indicators are readable in the flight environment.                                                                                         | Demonstration          | HIPI.5                | See HIPI.5                            |

| HIPI.5.4     | The HiPI Ground Crew Cockpit<br>Status Indicators shall reside on the<br>instrument panel.                                                                         | The cockpit layout is defined in the Cockpit ICD (ICD-CEPT-006).                                                                                   | Inspection             | HiPI.5                | See HIPI.5                            |

| HIPI.5.4.1   | HIPI-A shall illuminate status<br>indicators on the Ground Crew<br>Cockpit Status Indicator display for<br>HLMCs 1, 3, 5, 8, 10, 12.                               | The Ground Crew Cockpit<br>Indicator displays the status for all<br>A bus HLMCs (See Table 2,<br>Cockpit Ground Crew Cockpit<br>Status Indicator). | Demonstration          | HIPI.5.4              | See HIPI.5                            |

| HIPI.5.4.1.1 | HIPI-A shall illuminate 3 status<br>indicators on the Ground Crew<br>Cockpit Status Indicator for each<br>HLMC.                                                    | HIPI-A encompasses six HLMCs.<br>Each HLMC has three status<br>indicators (blue, green, red) for a<br>total of 18 indicators.                      | Demonstration          | HIPI.5.4.1            | See HIPI.5                            |

| Req. #       | Requirement                                                                                                                                                  | Rationale                                                                                                                                                      | Verification<br>Method | Requirements<br>Trace | Safety<br>Critical |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------|--------------------|

| HIPI.5.4.2   | HIPI-B shall illuminate status<br>indicators on the Ground Crew<br>Cockpit Status Indicator display for<br>HLMCs 2, 4, 6, 7, 9, 11.                          | The Ground Crew Cockpit Status<br>Indicator displays the status for all<br>B bus HLMCs (See Table 2,<br>Ground Crew Cockpit Status<br>Indicator).              | Demonstration          | HIPI.5.4              | See HIPI.5         |

| HIPI.5.4.2.1 | HIPI-B shall illuminate 3 status<br>indicators on the Ground Crew<br>Cockpit Status Indicator for each<br>HLMC.                                              | HIPI-B encompasses six HLMCs.<br>Each HLMC has three status<br>indicators (blue, green, red) for a<br>total of 18 indicators.                                  | Demonstration          | HIPI.5.4.2            | See HIPI.5         |

| HIPI.5.4.3   | The HiPI Ground Crew Cockpit<br>Status Indicators shall follow the<br>layout configuration as defined in the<br>Cockpit ICD (ICD-CEPT-006) Rev B<br>Page 56. | The cockpit layout is defined in the Cockpit ICD (ICD-CEPT-006).                                                                                               | Inspection             | HIPI.5                | See HIPI.5         |

| HIPI.5.4.3.1 | The HiPI Ground Crew Cockpit<br>Status Indicator labeling shall meet<br>the requirements defined in MIL-<br>STD-1472H, section 5.4.2 through<br>5.4.3.       | MIL-STD-1472H dictates this as a<br>Human Systems Integration<br>Requirement.                                                                                  | Inspection             | HIPI.5.4.3            | See HIPI.5         |

| HIPI.5.5     | The HiPI Pilot Cockpit Status<br>Indicators shall reside on the<br>instrument panel.                                                                         | The cockpit layout is defined in the Cockpit ICD (ICD-CEPT-006).                                                                                               | Inspection             | HIPI.5                | See HIPI.5         |